## VU2 185.324

Compilation Techniques for VLIW Architectures

Dietmar Ebner ebner@complang.tuwien.ac.at Florian Brandner brandner@complang.tuwien.ac.at

http://complang.tuwien.ac.at/cd/vliw

Ebner, Brandner | Compilation Techniques for VLIWs | SS08 Slide #1

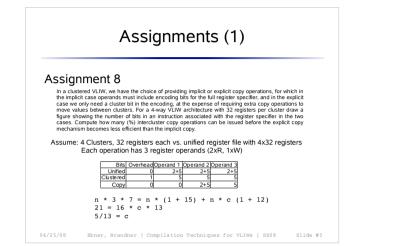

| Assignments (3)                                                                                                                                               |                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

|                                                                                                                                                               | ified register file with 32-bit registers (r0-r31), and |

| registers (p0-p7), and according comparison opera<br>using load/store operations (ld, st). The archit<br>select instruction. There are no restrictions on the | · · · · · · · · · · · · · · · · · · ·                   |

|                                                                                                                                                               | foo: r0 = UINT_MAX;<br>p0 = r2 == 0;                    |

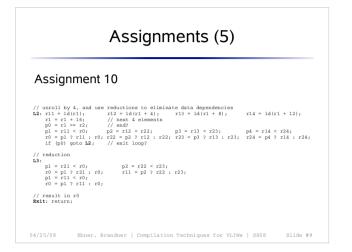

| Assignments (4)<br>Assignment 10<br>– Unrolling with pre-conditioning, reductions and ILP                                                                                                |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                                                                                                                                                          |  |  |

| <pre>// pre-conditioning<br/>L0: r3 = 1d(r1); r1 = r1 + 4; r10 = r10 - 1;<br/>p1 = r10 != 0;<br/>nop // wait for load<br/>p1 = r3 &lt; r0;<br/>if (p1) goto L0; r0 = p1 ? r3 : r0;</pre> |  |  |

| <pre>// prepare for unrolled loop<br/>L1: p0 = r2 == 0;</pre>                                                                                                                            |  |  |

| 04/25/08 Ebner, Brandner   Compilation Techniques for VLIWs   SS08 Slide #8                                                                                                              |  |  |

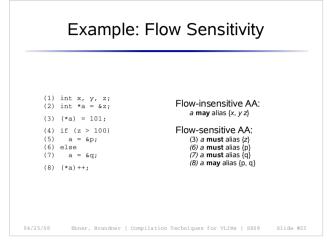

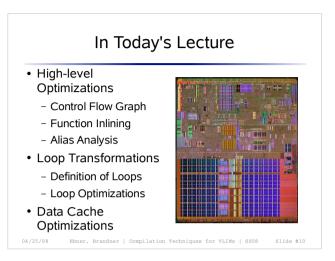

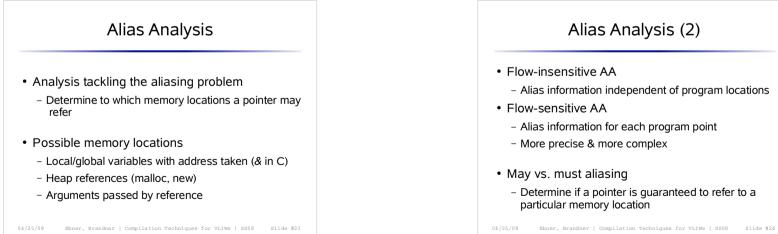

- Flow-insensitive AA

- Alias information independent of program locations

- Flow-sensitive AA

- Alias information for each program point

- More precise & more complex

- May vs. must aliasing

- Determine if a pointer is guaranteed to refer to a particular memory location