## VU2 185.324

Compilation Techniques for VLIW Architectures

Dietmar Ebner ebner@complang.tuwien.ac.at Florian Brandner brandner@complang.tuwien.ac.at

http://complang.tuwien.ac.at/cd/vliw

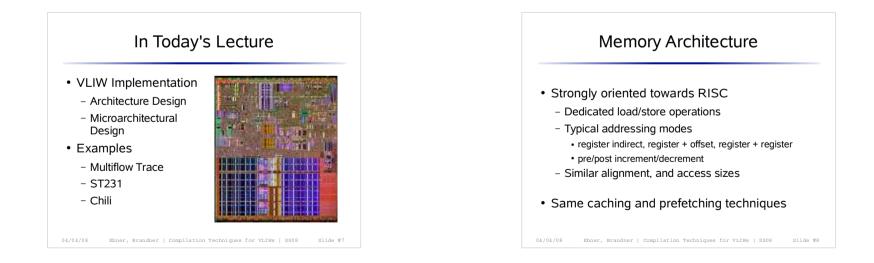

| Last Lecture (4) |                   |           |             |                   |           |                   |           |          |

|------------------|-------------------|-----------|-------------|-------------------|-----------|-------------------|-----------|----------|

|                  | Instruction/Group |           |             | Instruction/Group |           | Instruction/Group |           |          |

|                  | Bundle            |           |             | Bundle            |           |                   |           |          |

|                  | Operation         |           | Operation   | Operation         |           | Operation         | Operation |          |

|                  |                   | <u> </u>  | <u> </u>    |                   |           | <u> </u>          | <u> </u>  |          |

|                  | Syllable          | Syllable  | Syllable    | Syllable          | Syllable  | Syllable          | Syllable  |          |

| 04/04/           | 0.8 Eb            | ner. Bran | dner   Comr | vilation T        | echniques | for VLIWs         | 5508      | Slide #5 |

## · Benefits unclear

4/04/08 Ebner, Brandner | Compilation Techniques for VLIWs | SS08 Slide #25

## **Branch Architecture**

- Again similar to RISC

- Common prediction techniques

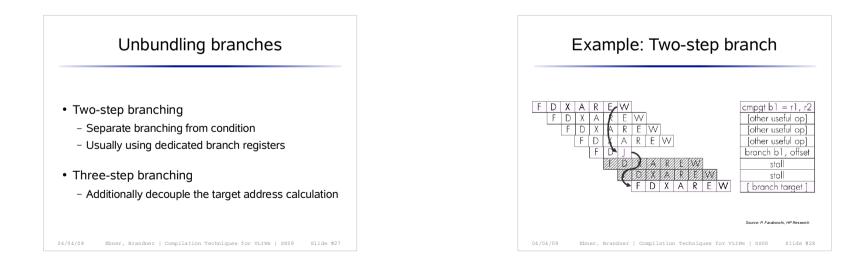

- Unbundling branches

- Split the branch into several steps

- Prepare the target instruction streams to fetch

- Select the instruction stream that will be taken

- Execute the taken instructions

- May only reside in the first syllable

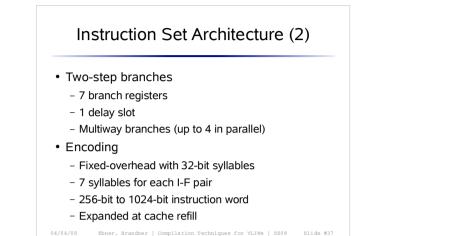

- Two-step branches

- 8 branch registers

- 2 bundle distance between condition and branch

- No delay slot

- All branches incur 1 stall cycle

04/04/08 Ebner, Brandner | Compilation Techniques for VLIWs | SS08 Slide #57

- Bundles of up to 4 syllables

- Distributed encoding

- Positional dispatch

- 32 bit syllables, 1 stop bit

- Immediates

- 9-bit short immediate

- 9+23-bit extended immediates

- Restrictions for

- Branches, multiplies, extended immediates